科技引領 擘畫新篇 2025年特殊食品行業科技與產業發展十大標志性事件發布

2025年,特殊食品行業在科技創新與產業變革的雙輪驅動下,迎來了一系列具有里程碑意義的突破與進展。這些事件不僅標志著行業技術水平的顯著躍升,更為未來健康產業的發展擘畫了清晰藍圖。以下是基于技術開發視角梳理的年度十大標志性事件:

- 精準營養3.0平臺實現商業化應用:首個整合多組學數據(基因組、代謝組、微生物組)、AI動態算法與實時可穿戴設備監測的個性化營養干預平臺正式投入市場,為特醫食品、嬰幼兒配方食品等領域的精準定制提供了核心技術支撐。

- 合成生物技術成功量產高純度人乳寡糖(HMOs)關鍵組分:通過先進的細胞工廠與酶催化技術,實現了過去難以獲取或成本極高的多種人乳寡糖的大規模、低成本綠色合成,打破了國外技術壟斷,為下一代嬰幼兒配方奶粉的升級奠定了原料基礎。

- 連續流智能制造產線在特醫食品工廠全面落地:采用模塊化、連續化、數字化控制的全新生產工藝,取代傳統批次生產,大幅提升了特醫食品的生產效率、穩定性和安全性,實現了從投料到成品的全程可追溯與智能化管控。

- 基于腸道菌群靶向調控的特定全營養配方食品獲批上市:針對腫瘤、糖尿病等特定疾病狀態下的營養不良,首款通過臨床驗證的、具有明確菌群調節功能的特殊醫學用途配方食品獲得監管批準,標志著營養干預進入“微生物組+”時代。

- AI輔助配方設計與功效預測系統投入使用:深度學習模型能夠根據目標人群的生理參數和健康需求,自動模擬并優化食品配方,大幅縮短了新產品研發周期,并提高了配方的科學性與有效性。

- 超高壓協同脈沖電場新型滅菌技術實現產業化:該技術在最大限度保留特醫食品中熱敏性營養素和生物活性成分的達到了商業無菌要求,解決了傳統熱加工帶來的品質劣變難題。

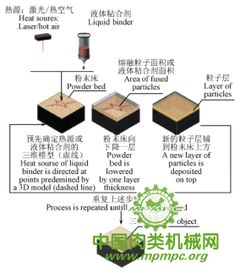

- 3D打印個性化營養膳食實現醫院場景規模化供應:針對吞咽障礙、術后康復等患者,能夠根據其個體營養需求和吞咽能力,實時打印出性狀、質地、營養成分均精準定制的營養膳食,提升了臨床喂養的依從性與效果。

- 全鏈條數字化質量管控平臺建成:利用區塊鏈和物聯網技術,構建了從原料溯源、生產過程、物流配送到臨床使用的特殊食品全生命周期質量數據閉環,實現了透明化、不可篡改的質量管理體系。

- 新型遞送系統提升功能因子生物利用度取得關鍵突破:通過納米乳化、微膠囊包埋等前沿技術,成功解決了多種維生素、益生菌、多肽等活性成分在特醫食品中的穩定性與靶向釋放問題,顯著提升了產品的實際功效。

- 行業首個“未來食品”開放創新平臺啟動:由政府、龍頭企業、頂尖科研院所共同發起,聚焦于細胞培養營養素、智能感知包裝、腦-腸軸靶向食品等前沿方向,旨在構建產學研用協同的下一代特殊食品技術開發生態。

這十大事件,深刻體現了2025年特殊食品行業以科技為引擎,向更精準、更智能、更高效、更個性化方向發展的強勁趨勢。它們不僅是技術開發的成果,更是產業升級的催化劑,共同擘畫出一幅以科技創新滿足人民日益增長的健康需求、引領行業高質量發展的嶄新篇章。

如若轉載,請注明出處:http://www.bibisoft.com.cn/product/56.html

更新時間:2026-03-19 14:24:05